- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC18C858T-I/PT (Microchip Technology)IC MCU OTP 16KX16 CAN 80TQFP

2000 Microchip Technology Inc.

Advanced Information

DS30475A-page 149

PIC18CXX8

15.4.1.2

Reception

When the R/W bit of the address byte is clear and an

address match occurs, the R/W bit of the SSPSTAT

register is cleared. The received address is loaded into

the SSPBUF register.

When the address byte overflow condition exists, then

no acknowledge (ACK) pulse is given. An overflow con-

dition is defined as either bit BF (SSPSTAT register) is

set or bit SSPOV (SSPCON1 register) is set.

An MSSP interrupt is generated for each data transfer

byte. Flag bit SSPIF (PIR registers) must be cleared in

software. The SSPSTAT register is used to determine

the status of the byte.

15.4.1.3

Transmission

When the R/W bit of the incoming address byte is set

and an address match occurs, the R/W bit of the

SSPSTAT register is set. The received address is

loaded into the SSPBUF register. The ACK pulse will

be sent on the ninth bit and pin RC3/SCK/SCL is held

low. The transmit data must be loaded into the

SSPBUF register, which also loads the SSPSR regis-

ter. Then pin RC3/SCK/SCL should be enabled by set-

ting bit CKP (SSPCON1 register). The master must

monitor the SCL pin prior to asserting another clock

pulse. The slave devices may be holding off the master

by stretching the clock. The eight data bits are shifted

out on the falling edge of the SCL input. This ensures

that the SDA signal is valid during the SCL high time

An MSSP interrupt is generated for each data transfer

byte. The SSPIF bit must be cleared in software and

the SSPSTAT register is used to determine the status

of the byte. The SSPIF bit is set on the falling edge of

the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the

master-receiver is latched on the rising edge of the

ninth SCL input pulse. If the SDA line is high (not ACK),

then the data transfer is complete. When the ACK is

latched by the slave, the slave logic is reset (resets

SSPSTAT register) and the slave monitors for another

occurrence of the START bit. If the SDA line was low

(ACK), the transmit data must be loaded into the SSP-

BUF register, which also loads the SSPSR register. Pin

RC3/SCK/SCL should be enabled by setting bit CKP.

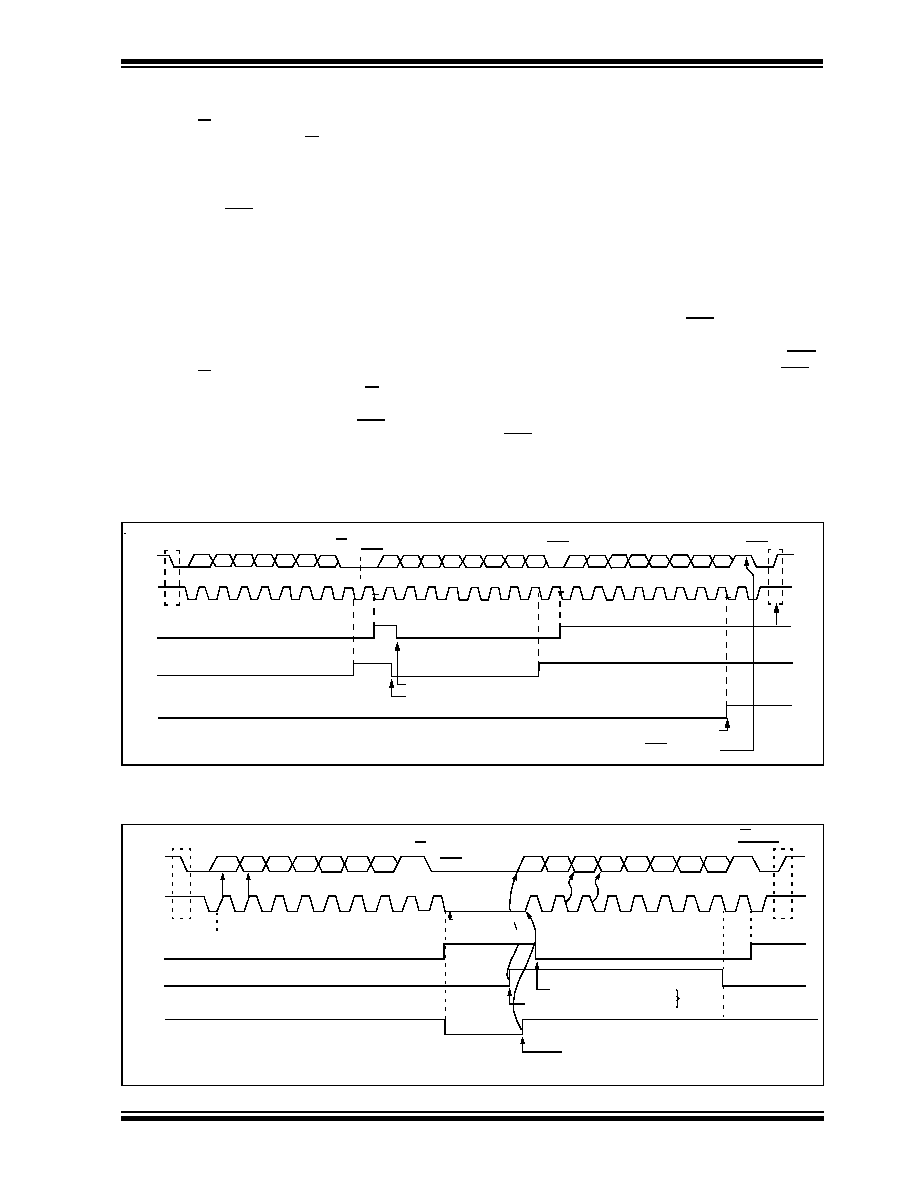

FIGURE 15-7: I2C SLAVE MODE WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

FIGURE 15-8: I2C SLAVE MODE WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

P

9

8

7

6

5

D0

D1

D2

D3

D4

D5

D6

D7

S

A7 A6 A5 A4 A3 A2 A1

SDA

SCL

1

2

3

456

78

9

12

34

56

7

8

9

12

3

4

Bus Master

Terminates

Transfer

Bit SSPOV is set because the SSPBUF register is still full.

Cleared in software

SSPBUF register is read

ACK

Receiving Data

D0

D1

D2

D3

D4

D5

D6

D7

ACK

R/W=0

Receiving Address

SSPIF

BF

SSPOV

Not ACK

ACK is not sent.

SDA

SCL

SSPIF

BF

CKP

A7

A6

A5

A4

A3

A2

A1

ACK

D7

D6

D5

D4

D3

D2

D1

D0

Not ACK

Transmitting Data

R/W = 1

Receiving Address

1

2

3

4

56

789

123

4

5

67

8

9

P

Cleared in software

SSPBUF is written in software

From SSP interrupt

service routine

Set bit after writing to SSPBUF

S

Data in

Sampled

SCL held low

while CPU

responds to SSPIF

(the SSPBUF must be written to

before the CKP bit can be set)

R/W = 0

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C658T-I/PT

IC MCU OTP 16KX16 CAN 64TQFP

PIC16LC717T-E/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC771T/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16C771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC770T/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC717T-I/SO

IC MCU OTP 2KX14 A/D PWM 18SOIC

PIC16LC771T/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

相关代理商/技术参数

PIC18F1220-E/ML

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/P

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SO

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SS

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/ML

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/P

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SO

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SS

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT